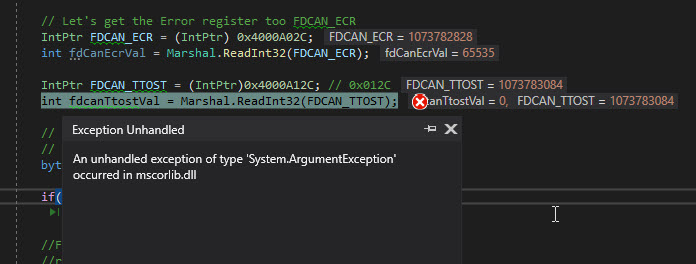

Those are all register you can access. TTOST is not on this list. And I don’t think you can find out something by this register which is only for CAN1.

uint CREL; /*!< FDCAN Core Release register, Address offset: 0x000 */

uint ENDN; /*!< FDCAN Endian register, Address offset: 0x004 */

uint RESERVED1; /*!< Reserved, 0x008 */

uint DBTP; /*!< FDCAN Data Bit Timing & Prescaler register, Address offset: 0x00C */

uint TEST; /*!< FDCAN Test register, Address offset: 0x010 */

uint RWD; /*!< FDCAN RAM Watchdog register, Address offset: 0x014 */

uint CCCR; /*!< FDCAN CC Control register, Address offset: 0x018 */

uint NBTP; /*!< FDCAN Nominal Bit Timing & Prescaler register, Address offset: 0x01C */

uint TSCC; /*!< FDCAN Timestamp Counter Configuration register, Address offset: 0x020 */

uint TSCV; /*!< FDCAN Timestamp Counter Value register, Address offset: 0x024 */

uint TOCC; /*!< FDCAN Timeout Counter Configuration register, Address offset: 0x028 */

uint TOCV; /*!< FDCAN Timeout Counter Value register, Address offset: 0x02C */

uint RESERVED2[4]; /*!< Reserved, 0x030 - 0x03C */

uint ECR; /*!< FDCAN Error Counter register, Address offset: 0x040 */

uint PSR; /*!< FDCAN Protocol Status register, Address offset: 0x044 */

uint TDCR; /*!< FDCAN Transmitter Delay Compensation register, Address offset: 0x048 */

uint RESERVED3; /*!< Reserved, 0x04C */

uint IR; /*!< FDCAN Interrupt register, Address offset: 0x050 */

uint IE; /*!< FDCAN Interrupt Enable register, Address offset: 0x054 */

uint ILS; /*!< FDCAN Interrupt Line Select register, Address offset: 0x058 */

uint ILE; /*!< FDCAN Interrupt Line Enable register, Address offset: 0x05C */

uint RESERVED4[8]; /*!< Reserved, 0x060 - 0x07C */

uint GFC; /*!< FDCAN Global Filter Configuration register, Address offset: 0x080 */

uint SIDFC; /*!< FDCAN Standard ID Filter Configuration register, Address offset: 0x084 */

uint XIDFC; /*!< FDCAN Extended ID Filter Configuration register, Address offset: 0x088 */

uint RESERVED5; /*!< Reserved, 0x08C */

uint XIDAM; /*!< FDCAN Extended ID AND Mask register, Address offset: 0x090 */

uint HPMS; /*!< FDCAN High Priority Message Status register, Address offset: 0x094 */

uint NDAT1; /*!< FDCAN New Data 1 register, Address offset: 0x098 */

uint NDAT2; /*!< FDCAN New Data 2 register, Address offset: 0x09C */

uint RXF0C; /*!< FDCAN Rx FIFO 0 Configuration register, Address offset: 0x0A0 */

uint RXF0S; /*!< FDCAN Rx FIFO 0 Status register, Address offset: 0x0A4 */

uint RXF0A; /*!< FDCAN Rx FIFO 0 Acknowledge register, Address offset: 0x0A8 */

uint RXBC; /*!< FDCAN Rx Buffer Configuration register, Address offset: 0x0AC */

uint RXF1C; /*!< FDCAN Rx FIFO 1 Configuration register, Address offset: 0x0B0 */

uint RXF1S; /*!< FDCAN Rx FIFO 1 Status register, Address offset: 0x0B4 */

uint RXF1A; /*!< FDCAN Rx FIFO 1 Acknowledge register, Address offset: 0x0B8 */

uint RXESC; /*!< FDCAN Rx Buffer/FIFO Element Size Configuration register, Address offset: 0x0BC */

uint TXBC; /*!< FDCAN Tx Buffer Configuration register, Address offset: 0x0C0 */

uint TXFQS; /*!< FDCAN Tx FIFO/Queue Status register, Address offset: 0x0C4 */

uint TXESC; /*!< FDCAN Tx Buffer Element Size Configuration register, Address offset: 0x0C8 */

uint TXBRP; /*!< FDCAN Tx Buffer Request Pending register, Address offset: 0x0CC */

uint TXBAR; /*!< FDCAN Tx Buffer Add Request register, Address offset: 0x0D0 */

uint TXBCR; /*!< FDCAN Tx Buffer Cancellation Request register, Address offset: 0x0D4 */

uint TXBTO; /*!< FDCAN Tx Buffer Transmission Occurred register, Address offset: 0x0D8 */

uint TXBCF; /*!< FDCAN Tx Buffer Cancellation Finished register, Address offset: 0x0DC */

uint TXBTIE; /*!< FDCAN Tx Buffer Transmission Interrupt Enable register, Address offset: 0x0E0 */

uint TXBCIE; /*!< FDCAN Tx Buffer Cancellation Finished Interrupt Enable register, Address offset: 0x0E4 */

uint RESERVED6[2]; /*!< Reserved, 0x0E8 - 0x0EC */

uint TXEFC; /*!< FDCAN Tx Event FIFO Configuration register, Address offset: 0x0F0 */

uint TXEFS; /*!< FDCAN Tx Event FIFO Status register, Address offset: 0x0F4 */

uint TXEFA; /*!< FDCAN Tx Event FIFO Acknowledge register, Address offset: 0x0F8 */

uint RESERVED7; /*!< Reserved, 0x0FC */